SignatureIP, the specialist in interconnect and interface solutions, announces early access availability of its cloud-based iNoCulator NoC design tool. Available at iNoCulator.ai, it is said to be “the first cloud-based platform for design of a Network on Chip (NoC)”. A NoC provides the interconnect infrastructure between key compute, storage, memory and I/O blocks in a semiconductor chip.

SignatureIP, the specialist in interconnect and interface solutions, announces early access availability of its cloud-based iNoCulator NoC design tool. Available at iNoCulator.ai, it is said to be “the first cloud-based platform for design of a Network on Chip (NoC)”. A NoC provides the interconnect infrastructure between key compute, storage, memory and I/O blocks in a semiconductor chip.

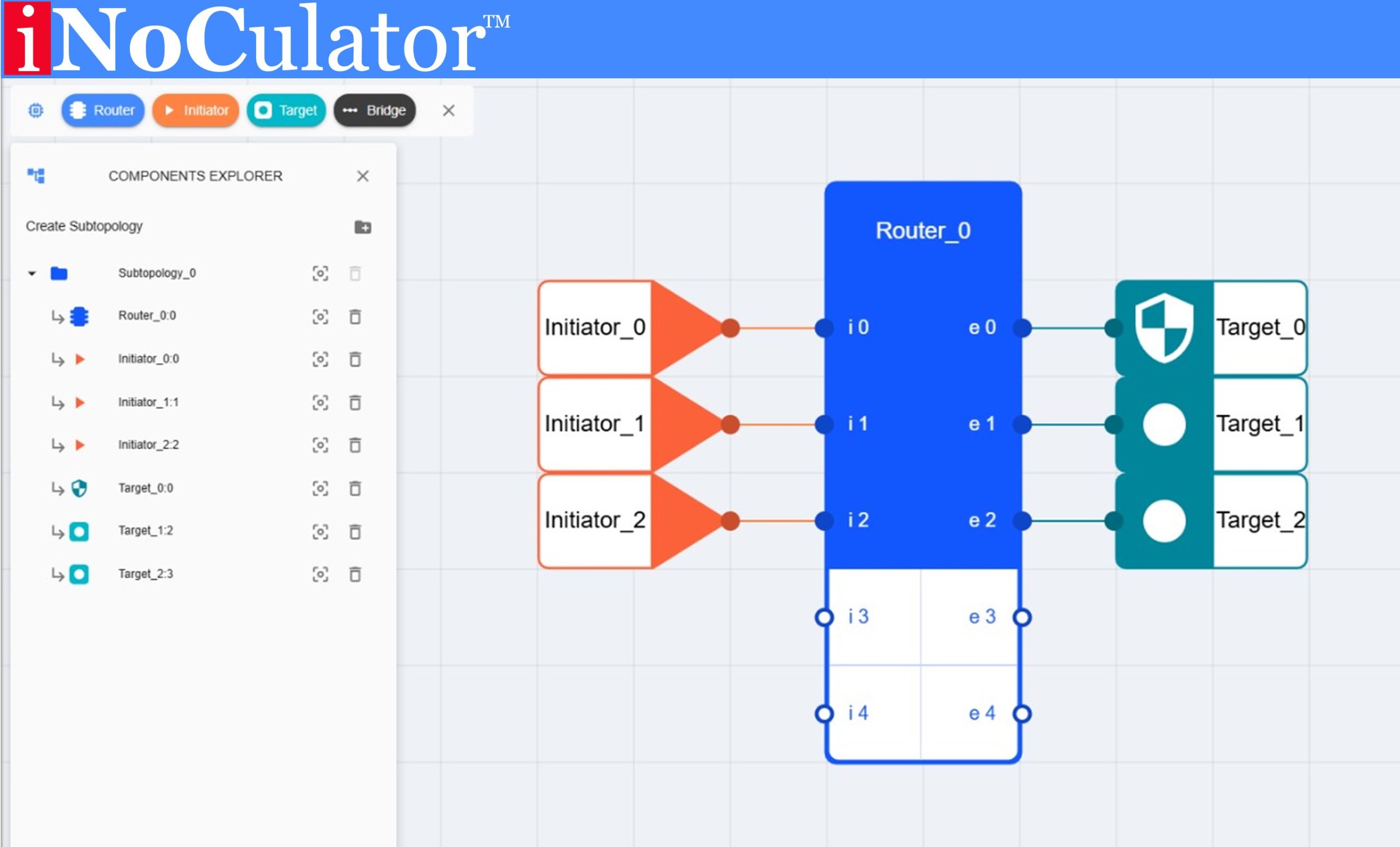

The iNoCulator tool simplifies the process of interconnect design from architectural exploration to RTL generation and physical implementation. Its cloud-based interface makes it fast and easy to get up and running, and the tool’s intelligent capabilities enable users to rapidly find an optimal NoC configuration to reduce costs and speed their time to market.

Purna Mohanty, CEO, SignatureIP, said, “At SignatureIP we are making NoC design accessible, fast and configurable. Today’s chip designs are becoming increasingly complex, but our novel tool reduces the complexity. Because our tool is cloud-based, architects and engineers can get going quickly via a simple evaluation agreement, with no need for lengthy negotiations with their finance or legal teams, and no need to wait for IT to install any software.”

How iNoCulator works

With iNoCulator, users can explore the design space at the top level of their chip before making major architectural decisions. They can easily change the NoC topology, experiment with different configuration settings, and instantly simulate the results to optimize the top-level design.

The system architect simply sets the target power, performance, area and timings into iNoCulator, and the tool creates possible topologies that can be easily and quickly tweaked to find the optimal solution. Built-in intelligent capabilities automate and speed up many of the processes involved in scenario building that would have otherwise required manual configuration. The result is an optimized, custom-configured NoC design delivered in clear, readable Register Transfer Level (RTL) format.

SignatureIP provides support to help customers understand the full range of available features.

Flexibility for today’s complex designs

The iNoCulator tool is processor-agnostic so it can be used with Arm, RISC-V or other processors. It can connect other on-chip IP blocks such as PCIe, CXL, and AI acceleration, enabling designers to create complex, high-performance heterogeneous systems on chips (SoCs) that can support a wide range of applications, from data centre acceleration to edge AI devices.

iNoCulator can generate NoCs in a variety of topologies, supporting multiple protocols, bus widths, and clocking and power control schemes that integrate easily with block-level RTL designs. It also has support for popular interface protocols (AXI, AHB, APB, SRAM) and various bus widths. The multiple clocking schemes include GALS, and the power control has power island generation and UPF output. It creates a layered, scalable, physically aware network.

The tool has multi-factor authentication, and each customer’s designs are secured in their own private area with no access from other users or from SignatureIP unless requested. iNoCulator is multi-user enabled for collaborative engineering.

Pricing and Availability

The iNoCulator platform is available now at iNoCulator.ai. Customers can register for an evaluation period of two weeks at no charge (with the possibility of extending the trial period upon request). After initial evaluation, customers can take an annual subscription license that can be used for interactive architectural exploration of any number of designs. This includes full access to all aspects of the tool and enables downloading final RTL with a per design license fee.

For more information about iNoCulator, visit https://www.signatureip.ai/iNoCulator.